公司简介

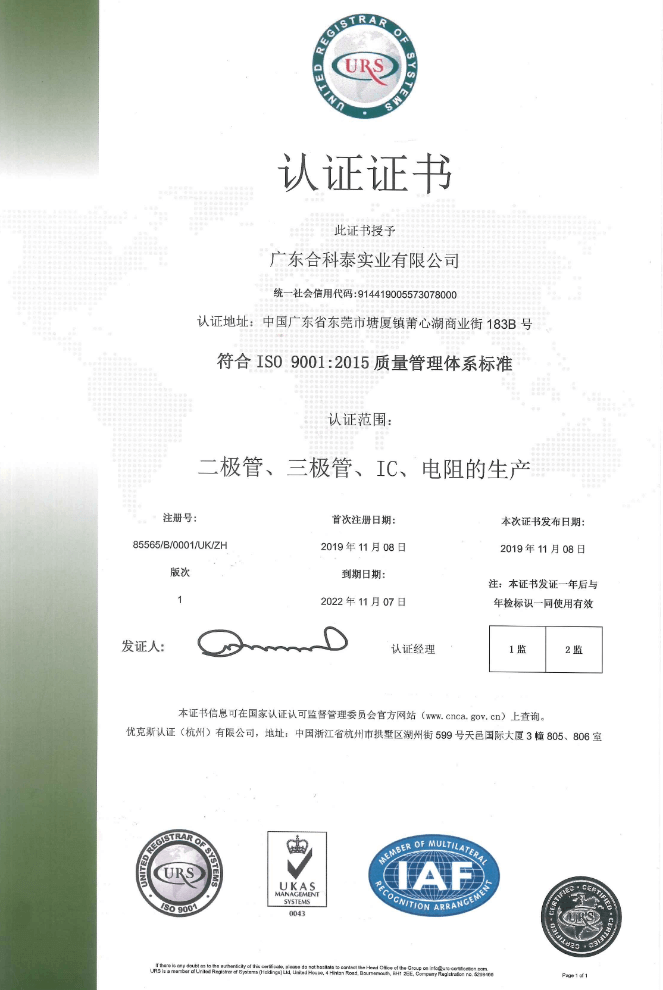

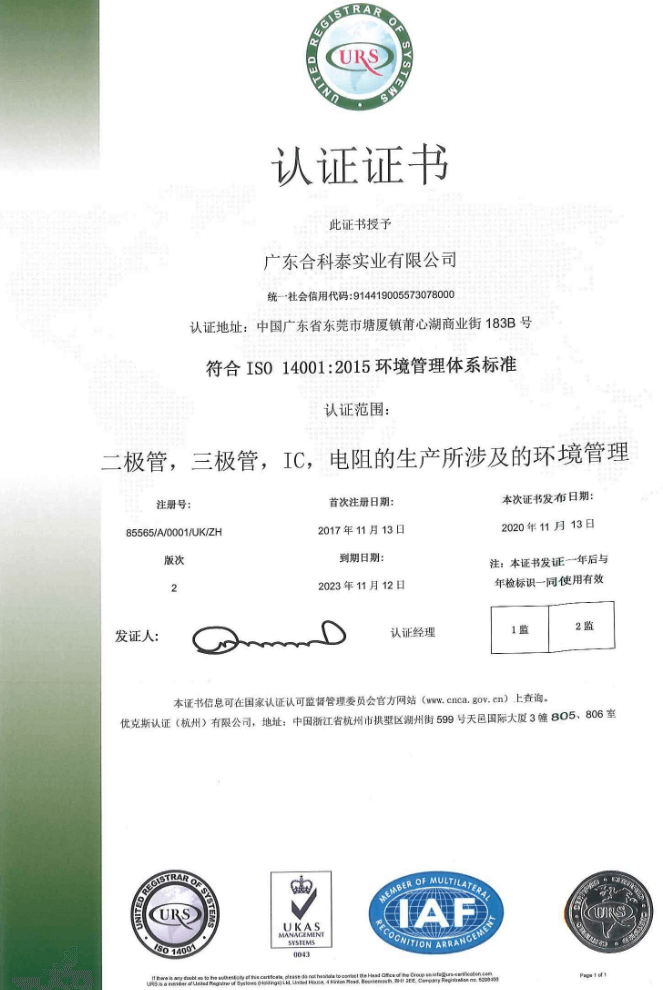

深圳市合科泰电子有限公司作为合科泰集团总部,1992 年初创于美丽鹏城深圳,专业从事半导体模拟芯片、集成电路、分立器件及被动元件的研发设计和销售,是深圳市专精特新和国家级高新技术企业……

30年+

行业沉淀

5万+

客户积累

60个+

服务国家与地区

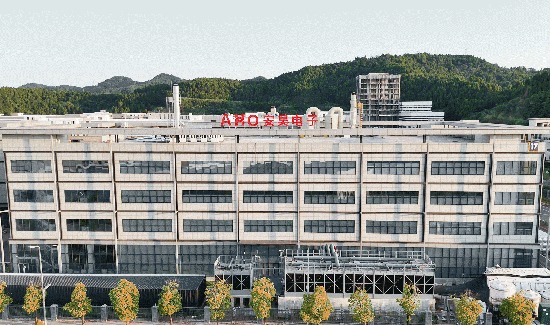

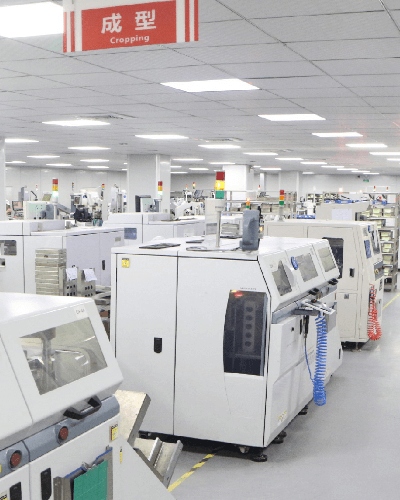

两大区域智能制造中心

华南制造基地位于惠州市博罗县,厂房面积80000平方米,西南制造基地位于四川南充市顺庆区,厂房面积40000平方米。

行业方案

新闻与活动

公司新闻

实力加冕 | 合科泰荣膺第二十三届“深圳(湾区)知名品牌”

这一次的获评高度肯定了合科泰的产品可靠性、市场口碑及品牌建设的综合实力,让合科泰朝着高质量发展的道路迈入。这份荣誉作为一个里程碑和新的起点,合科泰会以此不断强化品牌建设,致力于为客户提供更可靠和具有市场竞争力的产品,助力电子元器件产业的高质量发展。

2026-05-12 17:43:17

公司新闻

合科泰子公司喜报 | 四川顺芯半导体荣获“最佳品牌企业奖”,原厂封测实力获权威认可!

近日,2026年中国国际半导体先进封测大会于3月22-23日在上海举办,合科泰集团旗下四川顺芯半导体有限公司荣获“最佳品牌企业奖”。该奖项旨在表彰封测技术、品质管理、市场口碑以及品牌影响力方面有杰出表现的企业。

2026-03-24 15:06:44

公司新闻

合科泰春茗家宴 | 遇到接地气老板是一种什么体验?

今年年会,让我彻底明白了一件事:好的老板,不仅会带着你拼事业,更懂得陪你一起好好玩。 没有冰冷的致辞,没有尴尬的应酬,也没有形式主义的流程。只有一群人、满屋的笑声、从头到尾的轻松与自在,这才该是年会真正的样子。

2026-03-24 14:56:52

公司新闻

凝心聚力·启新程 | 合科泰集团2025年度总结及2026年发展规划执行大会圆满召开

2026年1月19日至20日,合科泰集团2025年度总结及2026年发展规划执行大会在深圳康利城和南充制造中心同步举行。本次大会全面复盘2025年集团经营管理成果,明确2026年发展战略与目标,为集团在新的一年里破浪前行、再攀高峰奠定了坚实基础。

2026-01-22 15:27:06

公司新闻

合科泰2026年春节放假通知及备货提醒!

根据国家法定节假日休假规定,结合公司的实际情况,现就2026年春节放假作如下安排: 深圳合科泰(含康利城和138物流)放假时间为:2026年2月11日(腊月二十四,星期三)至2026年2月24日(正月初八,星期二)放假,共14天。 其中,2月28日(周六)正常上班和2月23日(周一)对调,2月16日、17日、18日、19日为国家法定节假日。2月25日(正月初九,星期三)准时上班。

2026-01-22 14:40:40